# APPENDIX A. (Continued) P2 CONNECTOR PIN ASSIGNMENT OF OPTIONAL BUS SIGNALS

|                                                                      | (CO                                                               | MPONENT SIDE)                                                                                                  |                                                                      | (0                                                                     | CIRCUIT SIDE)                                                                                                |

|----------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| PIN                                                                  | MNEMONIC                                                          | DESCRIPTION                                                                                                    | PIN                                                                  | MNEMONIC                                                               | DESCRIPTION                                                                                                  |

| 1<br>3<br>5<br>7<br>9<br>11<br>13                                    | GND<br>5 VB<br>-5 VB<br>12 VB<br>PFSR/                            | Signal GND<br>+5V Battery<br>Reserved<br>-5V Battery<br>Reserved<br>+12V Battery<br>Power Fail Sense Reset     | 2<br>4<br>6<br>8<br>10<br>12                                         | GND<br>5 VB<br>VCCPP<br>-5 VB<br>Reserved<br>12 VB<br>Reserved         | Signal GND<br>+5V Battery<br>+5V Pulsed Power<br>-5V Battery<br>+12V Battery                                 |

| 15<br>17<br>19<br>21<br>23<br>25<br>27<br>29<br>31<br>33<br>35<br>37 | -12 VB<br>PFSN/<br>PFIN/<br>GND<br>+15V<br>-15V<br>PAR1/<br>PAR2/ | -12V Battery<br>Power Fail Sense<br>Power Fail Interrupt<br>Signal GND<br>+15V<br>-15V<br>Parity 1<br>Parity 2 | 16<br>18<br>20<br>22<br>24<br>26<br>28<br>30<br>32<br>34<br>36<br>38 | -12 VB ACLO MPRO/ GND +15V -15V -15V ALT WAIT/ ALE Reserved AUX RESET/ | -12V Battery AC Low Memory Protect Signal GND +15V -15V Bus Master HALT Bus Master WAIT STATE Bus Master ALE |

| 39<br>40<br>43<br>45<br>47<br>49<br>51<br>53<br>55<br>57             | Reserved                                                          |                                                                                                                | 40<br>42<br>44<br>46<br>48<br>50<br>52<br>54<br>56<br>58<br>60       | Reserved                                                               | Reset switch                                                                                                 |

### Notes:

- 1. PFIN, on slave modules, if possible, should have the option of connecting to INT0/ on P1. 2. All undefined pins are reserved for future use.

All Mnemonics © Intel Corporation 1978

APPENDIX B

BUS TIMING SPECIFICATIONS SUMMARY

| Parameter          | Description                                                                                                   | Minimum                  | Maximum                     | Units |

|--------------------|---------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------|-------|

| tBCY               | Bus Clock Period                                                                                              | 100                      | D.C.                        | ns    |

| tBW tBW            | Bus Clock Width                                                                                               | 0.35 t <sub>BCY</sub>    | 0.65 t <sub>BCY</sub>       |       |

| <sup>t</sup> SKEW  | BCLK/skew                                                                                                     |                          | 3                           | ns    |

| tPD .              | Standard Bus<br>Propagation Delay                                                                             |                          | 3                           |       |

| <sup>t</sup> AS    | Address Set-Up Time<br>(at Slave Board)                                                                       | 50                       |                             | ns    |

| tps                | Write Data Set ·<br>Up Time                                                                                   | 50                       |                             | ns    |

| <sup>t</sup> AH    | Address Hold Time                                                                                             | 50                       |                             | ns    |

| tDHW               | Write Data Hold Time                                                                                          | 50                       |                             | ns    |

| <sup>t</sup> DXL   | Read Data Set<br>Up Time To XACK                                                                              | 0                        |                             | ns    |

| <sup>t</sup> DHR   | Read Data Hold Time                                                                                           | 0                        | 65                          | ns    |

| <sup>†</sup> XAH   | Acknowledge Hold<br>Time                                                                                      | 0                        | 65                          | ns    |

| <sup>t</sup> XACK  | Acknowledge Time                                                                                              | 0                        | tтоит                       | ns    |

| <sup>t</sup> CMD   | Command Pulse<br>Width                                                                                        | 100                      | <sup>t</sup> TOUT           | ns    |

| t <sub>ID</sub>    | Inhibit Delay                                                                                                 | 0                        | 100<br>(Recommend < 100 ns) | ns    |

| <sup>t</sup> XACKA | Acknowledge Time of<br>of an Inhibited Slave                                                                  | t <sub>IAD</sub> + 50 ns | <sup>t</sup> TOUT           |       |

| <sup>†</sup> XACKB | Acknowledge Time of<br>an Inhibiting Slave                                                                    | 1.5                      | <sup>t</sup> TOUT           | μs    |

| <sup>†</sup> IAD   | Acknowledge Disable from Inhibit (An internal parameter on an inhibited slave; used to determine tXACKA Min.) | 0                        | 100<br>(arbitrary)          | ns    |

| <sup>†</sup> AIZ   | Address to Inhibits<br>High delay                                                                             |                          | 100                         | ns    |

| tINTA              | INTA/ Width                                                                                                   | 250                      |                             | ns    |

| <sup>t</sup> CSEP  | Command Separation                                                                                            | 100                      |                             | ns    |

# APPENDIX B (Continued) BUS TIMING SPECIFICATIONS SUMMARY

| Parameter          | Description                                                           | Minimum   | Maximum                                  | Units |

|--------------------|-----------------------------------------------------------------------|-----------|------------------------------------------|-------|

| <sup>†</sup> BREQL | ∔BCLK/ to BREQ/<br>Low Delay                                          | 0         | 35                                       | ns    |

| <sup>†</sup> BREQH | ∔BCLK / to BREQ /<br>High Delay                                       | 0         | 35                                       | ns    |

| †BPRNS             | BPRN / to ↓BCLK /<br>Setup Time                                       | 22        |                                          | ns    |

| <sup>t</sup> BUSY  | BUSY/ delay<br>from ∔BCLK/                                            | 0         | 70                                       | ns    |

| <sup>t</sup> BUSYS | BUSY/ to \BCLK/<br>Setup Time                                         | 25        |                                          | ns    |

| <sup>t</sup> BPRO  | #BCLK/ to BPRO/<br>(CLK to Priority Out)                              | 0         | 40                                       | ns    |

| <sup>†</sup> BPRNO | BPRN / to BPRO /<br>(Priority In to Out)                              | 0         | 30                                       | ns    |

| <sup>t</sup> CBRO  | ↓BCLK/ to CBRQ/<br>(CLKto Common<br>Bus Request)                      | 0         | 60                                       | ns    |

| <sup>†</sup> CBRQS | CBRQ/ to ↓BCLK/<br>Setup Time                                         | 35        |                                          | ns    |

| tCPM               | Central Priority<br>Module Resolution<br>Delay (Parallel<br>Priority) | 0         | ¹BCY-¹BREQ<br>-2tpD<br>-¹BPRNS<br>-¹SKEW |       |

| tCCY               | C-clock Period                                                        | 100       | 110                                      | ns    |

| tcw                | C-clock Width                                                         | 0.35 tCCY | 0.65 t <sub>CCY</sub>                    | ns    |

| †INIT              | INIT/Width                                                            | 5         |                                          | ms    |

| INITS              | INIT/ to MPRO/<br>Setup Time                                          | 100       |                                          | ns    |

| tPBD               | Power Backup<br>Logic Delay                                           | 0         | 200                                      | ns    |

| tPFINW             | PFIN/ Width                                                           | 2.5       |                                          | ms    |

| <sup>t</sup> MPRO  | MPRO/ Delay                                                           | 2.0       | 2.5                                      | ms    |

| <sup>t</sup> ACLOW | ACLO/ Width                                                           | 3.0       |                                          | ms    |

| tpfsrw             | PFSR/ Width                                                           | 100       | 1                                        | ns    |

| tTOUT              | Timeout Delay                                                         | 5         | ∞                                        | ms    |

| †DCH               | D.C. Power Supply<br>Hold from ALCO/                                  | 3.0       |                                          | ms    |

| tDCS               | D.C. Power Supply<br>Setup to ACLO/                                   | 5         |                                          | ms    |

APPENDIX C

BUS DRIVERS, RECEIVERS, AND TERMINATIONS

| Driver 1,3                |                                                                               |      |                          |                           | Receiver 2,3                        |                                                                   |                          |                          | Termination                         |                                            |                  |            |        |

|---------------------------|-------------------------------------------------------------------------------|------|--------------------------|---------------------------|-------------------------------------|-------------------------------------------------------------------|--------------------------|--------------------------|-------------------------------------|--------------------------------------------|------------------|------------|--------|

| Bus Signals               | Location                                                                      | Туре | IOL<br>Min <sub>ma</sub> | IOH<br>Min <sub>µ</sub> a | C <sub>O</sub><br>Max <sub>p1</sub> | Location                                                          | liL<br>Max <sub>ma</sub> | IIH<br>Max <sub>µa</sub> | C <sub>I</sub><br>Max <sub>pf</sub> | Location                                   | Туре             | R          | Units  |

| DAT0/→DATF/<br>(16 lines) | Masters<br>and Slaves                                                         | TRI  | 16                       | -2000                     | 300                                 | Masters<br>and Slaves                                             | -0.8                     | 125                      | 18                                  | 1 place                                    | Pullup           | 2.2        | KΩ     |

| ADR0/-ADRB/,              | Masters                                                                       | TRI  | 16                       | -2000                     | 300                                 | Slaves                                                            | -0.8                     | 125                      | 18                                  | 1 place                                    | Pullup           | 2.2        | KΩ     |

| BHEN/<br>(21 lines)       |                                                                               |      |                          |                           |                                     |                                                                   |                          |                          |                                     |                                            |                  |            |        |

| MRDC/,MWTC/               | Masters                                                                       | TRI  | 32                       | -2000                     | 300                                 | Slaves<br>(Memory;<br>memory-<br>mapped I/O)                      | -2                       | 125                      | 18                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| IORC/,IOWC/               | Masters                                                                       | TRI  | 32                       | -2000                     | 300                                 | Slaves<br>(I/O)                                                   | -2                       | 125                      | 18                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| XACK/                     | Slaves                                                                        | TRI  | 32                       | -2000                     | 300                                 | Masters                                                           | -2                       | 125                      | 18                                  | 1 place                                    | Pullup           | 510        | Ω      |

| INH1/,INH2/               | Inhibiting<br>Slaves                                                          | ос   | 16                       | -                         | 300                                 | Inhibited<br>Slaves<br>(RAM, PROM,<br>ROM, Memory-<br>Mapped I/O) | -2                       | 50                       | 18                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| BCLK/                     | 1 place<br>(Master us)                                                        | TTL  | 48                       | -3000                     | 300                                 | Master                                                            | -2                       | 125                      | 18                                  | Mother-<br>board                           | To +5V<br>To GND | 220<br>330 | Ω<br>Ω |

| BREQ/                     | Each<br>Master                                                                | TTL  | 5                        | -400                      | 60                                  | Central<br>Priority<br>Module                                     | 2                        | 50                       | 18                                  | Central<br>Priority<br>Module<br>(not req) | Pullup           | 1          | KΩ     |

| BPRO/                     | Each<br>Master                                                                | TTL  | 5                        | -400                      | 60                                  | Next Master<br>in Serial<br>Priority<br>Chain at<br>its BPRN/     | -1.6                     | 50                       | 18                                  | (not req)                                  |                  |            |        |

| BPRN/                     | Parallel:<br>Central<br>Priority<br>Module<br>Serial:Prev<br>Masters<br>BPRO/ | TTL  | 5                        | -400                      | 300                                 | Master                                                            | -2                       | 50                       |                                     | (not req)                                  |                  |            |        |

| BUSY/, CBRQ               | All Masters                                                                   | O.C. | 32                       | _                         | 300                                 | All Masters                                                       | -2                       | 50                       | 18                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| INIT/                     | Master                                                                        | O.C. | 32                       | _                         | 300                                 | All                                                               | -2                       | 50                       | 18                                  | 1 place                                    | Puliup           | 2.2        | KΩ     |

| CCLK/                     | 1 place                                                                       | TTL  | 48                       | -3000                     | 300                                 | Any                                                               | -2                       | 125                      | 18                                  | Mother-<br>board                           | To +5V<br>To GND | 220<br>330 |        |

| INTA/                     | Masters                                                                       | TRI  | 32                       | -2000                     | 300                                 | Slaves<br>(Interrupting<br>I/O)                                   | -2                       | 125                      | 18                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| INT0/→INT7/<br>(8 lines)  | Slaves                                                                        | o.c. | 16                       | -                         | 300                                 | Masters                                                           | -1.6                     | 40                       | 18                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| PFSR/                     | User's Fron<br>Panel?                                                         | TTL  | 16                       | -400                      | 300                                 | Slaves,<br>Masters                                                | -1.6                     | 40                       | 18                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| PFSN/                     | Power Back<br>Up Unit                                                         | TTL  | 16                       | -400                      | 300                                 | Masters                                                           | -1.6                     | 40                       | 16                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| ACLO                      | Power<br>Supply                                                               | O.C. | 16                       | -400                      | 300                                 | Slaves,<br>Masters                                                | -1.6                     | 40                       | 18                                  | 1 place                                    | Pullup           | 1          | KΩ     |

| PFIN/                     | Power Back-<br>Up Unit                                                        | o.c. | 16                       | -400                      | 300                                 | Masters                                                           | -1.6                     | 40                       | 18                                  | 1 place                                    | Pullup           | 1          | ΚΩ     |

| MPRO/                     | Power Back-<br>Up Unit                                                        | TTL  | 16                       | -400                      | 300                                 | Slaves<br>Masters                                                 | -1.6                     | 40                       | 18                                  | 1 place                                    | Pullup           | 1          | ΚΩ     |

## **APPENDIX C (Continued) BUS DRIVERS, RECEIVERS, AND TERMINATIONS**

| Driver 1,3  |                           |                  |                          |                          | Receiver 2,3                        |          |                          | Termination               |                                     |          |      |   |       |

|-------------|---------------------------|------------------|--------------------------|--------------------------|-------------------------------------|----------|--------------------------|---------------------------|-------------------------------------|----------|------|---|-------|

| Bus Signals | Location                  | Туре             | IOL<br>Min <sub>ma</sub> | IOH<br>Min <sub>µa</sub> | C <sub>O</sub><br>Max <sub>pf</sub> | Location | liL<br>Max <sub>ma</sub> | IIH<br>Max <sub>µ</sub> a | C <sub>I</sub><br>Max <sub>pf</sub> | Location | Туре | R | Units |

| Aux Reset/  | User's<br>Front<br>Panel? | Switch<br>to GND | _                        | _                        | _                                   | Masters  | -2                       | 50                        | 18                                  | None     |      |   |       |

### Notes:

1. Driver Requirements

1<sub>OH</sub> = High Output Current Drive

IOL = Low Output Current Drive

CO = Capacitance Drive Capability

TRI = 3-State Drive

O.C. = Open Collector Driver

TTL = Totem-pole Driver

2. Receiver Requirements

I<sub>IH</sub> = High Input Current Load I<sub>IL</sub> = Low Input Current Load Ci = Capacitive Load

3. TTL low state must be ≥ -0.5v but ≤ 0.8v at the receivers TTL high state must be ≥ 2.0v but ≤ 5.5v at the receivers

4. For the iSBC 80/10 and the iSBC 80/10A use only a 1K pull-up resistor to +5v for BCLK/ and CCLK/ termination.

# APPENDIX D BUS POWER SPECIFICATIONS

|                                            |                                       | Standa                               | rd (P1)  |                | Optional (P2)  |                          |                  |                |                |          |  |

|--------------------------------------------|---------------------------------------|--------------------------------------|----------|----------------|----------------|--------------------------|------------------|----------------|----------------|----------|--|

|                                            |                                       |                                      |          |                | Analog         | Power Battery Power Back |                  |                |                | р        |  |

|                                            | Ground                                | + 5                                  | + 12     | - 12           | + 15           | 15                       | +5               | + 12           | - 12           | - 5      |  |

| Mnemonic                                   | GND                                   | + 5V                                 | + 12V    | - 12V          | + 15V          | – 15V                    | + 5B             | + 12B          | – 12B          | – 5B     |  |

| Bus Pins                                   | P1 + 1,2,<br>11,12,<br>75,76<br>85,86 | P1 + 3,4,<br>5,6,81,<br>82,83,<br>84 | P1 + 7,8 | P1 + 79,<br>80 | P2 + 23,<br>24 | P2 + 25,<br>26           | P2 + 3,4,<br>5,6 | P2 + 11,<br>12 | P2 + 15,<br>16 | P2 – 7,8 |  |

| Nominal Output                             | Ref.                                  | + 5.0V                               | + 12.0V  | - 12.0V        | + 15.0V        | - 15.0V                  | + 5.0V           | + 12.0V        | - 12.0V        | - 5.0V   |  |

| Tolerance from Nominal <sup>1</sup>        | Ref.                                  | ± 5%                                 | ± 5%     | ±5%            | ± 3%           | ± 3%                     | ±5%              | ± 5%           | ± 5%           | ±5%      |  |

| Ripple<br>(Pk-Pk)²                         | Ref.                                  | 50 mV                                | 50 mV    | 50 mV          | 10 mV          | 10 mV                    | 50 mV            | 50 mV          | 50 mV          | 50 mV    |  |

| Transient<br>Response<br>Time <sup>3</sup> |                                       | 500 μs                               | 500μs    | 500 μs         | 100 μs         | 100 μs                   | 500 μs           | 500 μs         | 500 μs         | 500 μs   |  |

| Transient<br>Deviation <sup>4</sup>        |                                       | ± 10%                                | ± 10%    | ± 10%          | ± 10%          | ± 10%                    | ± 10%            | ± 10%          | ± 10%          | ± 10%    |  |

### NOTES:

- 1. Tolerance is worst case, including initial voltage setting line and load effects of power source, temperature drift, and any additional steady state influences

- 2. As measured over any bandwidth not to exceed 0 to 500 kHz.

- 3. As measured from the start of a load change to the time an output recovers within  $\pm 0.1\%$  of final voltage.

- 4. Measured as the peak deviation from the initial voltage.

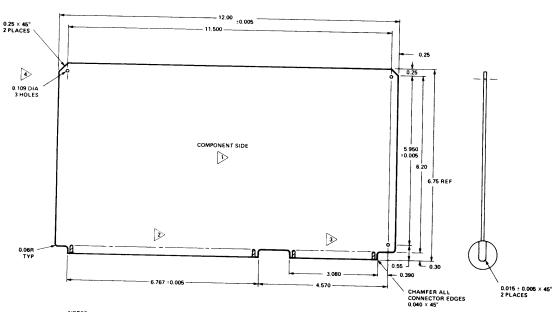

# APPENDIX E **MECHANICAL SPECIFICATIONS**

### NOTES

BOARD THICKNESS: 0.062

MULTIBUS CONNECTOR: 86-PIN, 0.156 SPACING CDC VFB01E43D00A1 VIKING 2VH43/1ANE5

3> AUXILIARY CONNECTOR: 60-PIN, 0.100 SPACING CDC VPB01B30D00A1 TI H311130 AMP PE5-14559

EJECTOR TYPE: SCANBE #S203

- BUS DRIVERS AND RECEIVERS SHOULD BE LOCATED AS CLOSE AS POSSIBLE TO THEIR RESPECTIVE MULTIBUS PIN CONNECTIONS

- BOARD SPACING: 0.6

- COMPONENT HEIGHT: 0.4

- CLEARANCE ON CONDUCTOR NEAR EDGES: 0.050

### APPENDIX F

### APPENDIX G

November 1978

# sing the ise vehicle code sing the children code and the children

©Intel Corporation, 1978

### I. INTRODUCTION

The iSBC 957 Intellec—iSBC 86/12 Interface and Execution Package contains the hardware and software required to interface an iSBC 86/12 Single Board Computer with an Intellec Microcomputer Development System. The iSBC 957 package gives the 8086 user the capability to develop software on an Intellec System and then debug this software on an iSBC 86/12 board using a program download capability and an interactive system monitor. The 8086 user has all the capabilities of the Intellec system at his disposal and has the powerful iSBC 86/12 system monitor commands to use for debugging 8086 programs.

The iSBC 86/12 board is an Intel 8086 based processor board which, in addition to the processor, contains 32K bytes of dual port RAM, sockets for up to 16K bytes of ROM/EPROM, a serial I/O port, 24 parallel I/O lines, 2 programmable counters, 9 levels of vectored priority interrupts, and an interface to the MULTIBUS™ system bus. The iSBC 957 package consists of monitor EPROMs for the iSBC 86/12 board, Loader software for the Intellec system, four (4) cable assemblies, assorted line drivers and terminators, and signal adapters. The iSBC 957 package provides the capability of downloading and uploading program and data blocks between an iSBC 86/12 board and an Intellec system. In addition, monitor commands and displays may be input and viewed from the Intellec system console. The iSBC 957 package, when used with the iSBC 86/12 board and an Intellec Microcomputer Development System, provides the user with the capability to edit, compile or assemble, link, locate, download, and interactively debug programs for the 8086 processor. The iSBC 957 package and the iSBC 86/12 board form an excellent "execution vehicle" for users developing software for the 8086 processor regardless of whether the users are 8086 component users or iSBC 86/12 board users. Using the iSBC 957 package 8086 programs may be debugged at the full 5 MHz speed of the processor. The recommended hardware for the execution vehicle is an iSBC 660 system chassis with an 8 card slot backplane and power supply, an iSBC 032 32K byte RAM memory board, the iSBC 957 package, and the iSBC 86/12 board.

This application note will describe how the iSBC 957 package may be used to develop and debug 8086 programs. First a description of the iSBC 86/12 board will be presented. Readers familiar

with the iSBC 86/12 board may want to skip this section. Next follows a detailed description of the iSBC 957 package and the iSBC 86/12 system monitor commands. A program example of a matrix multiplication routine will then be presented. This example will contain both assembly language and PL/M-86 procedures. The steps required to compile, assemble, link, locate and debug the program code will be explained in detail. A typical debugging session using the iSBC 86/12 system monitor will be presented.

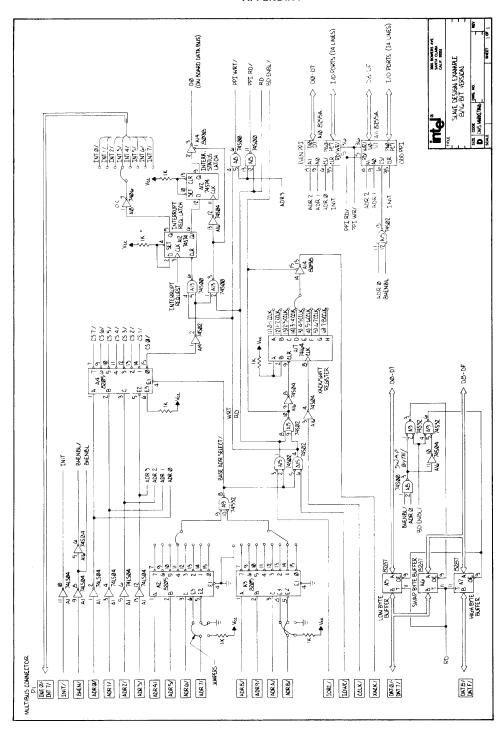

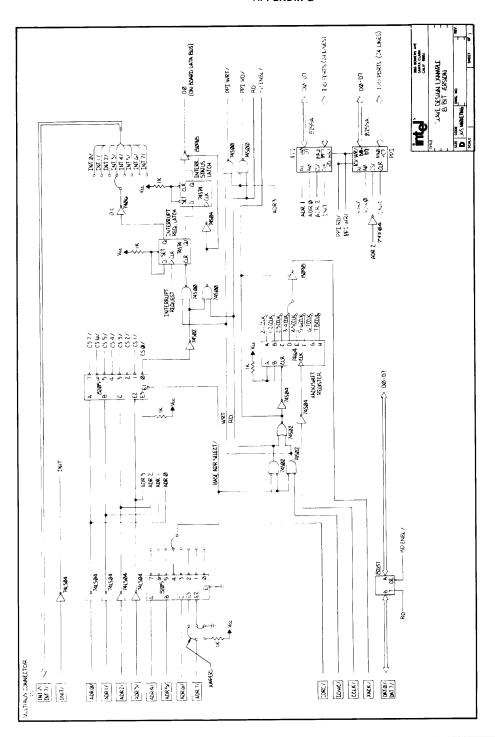

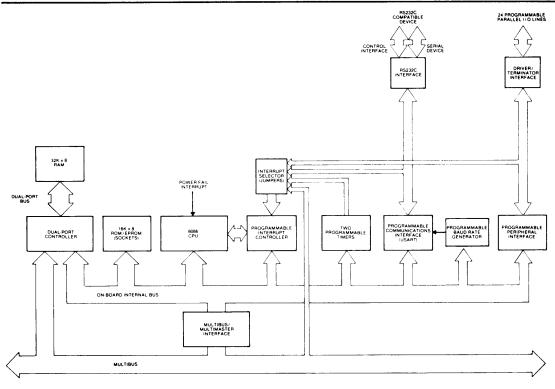

# II. THE iSBC™ 86/12 SINGLE BOARD COMPUTER

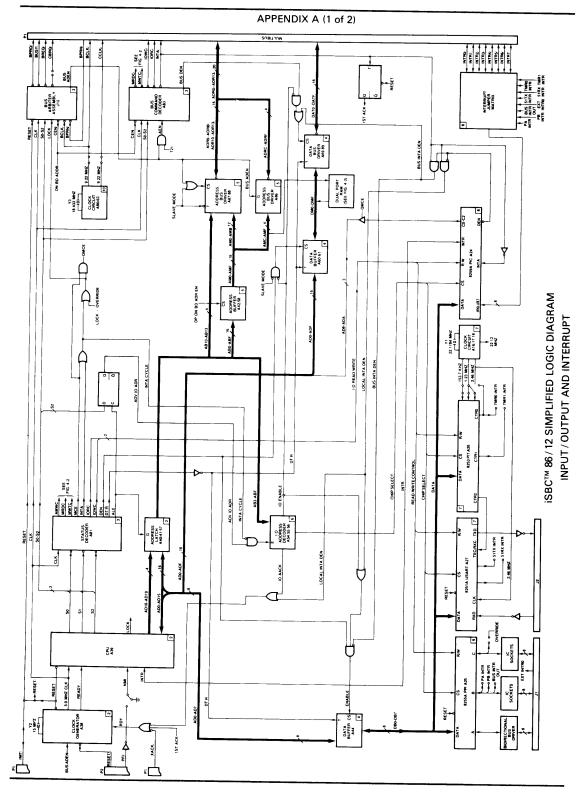

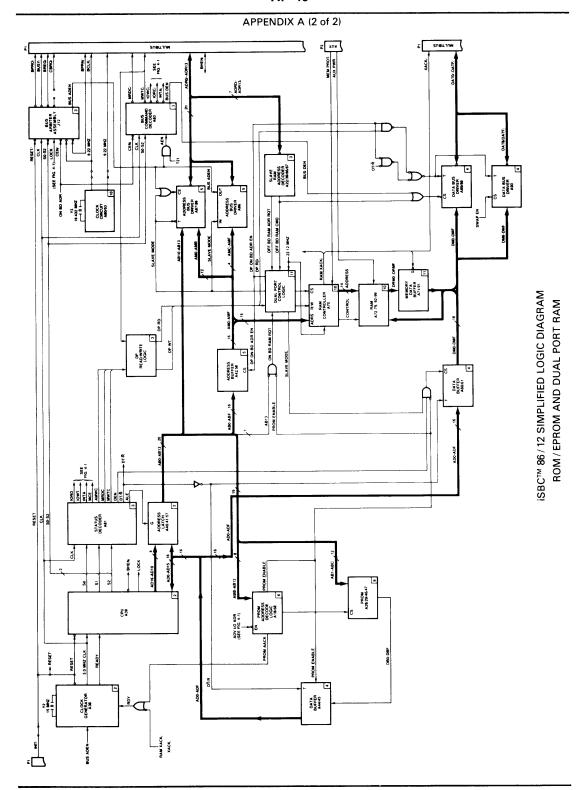

The iSBC 86/12 Single Board Computer, which is a member of Intel's complete line of iSBC 80/86 computer products, is a complete computer system on a single printed-circuit assembly. The iSBC 86/ 12 board includes a 16-bit central processing unit (CPU), 32K bytes of dynamic RAM, a serial communications interface, three programmable parallel I/O ports, programmable timers, priority interrupt control, MULTIBUS control logic, and bus expansion drivers for interface with other MULTIBUScompatible expansion boards. Also included is dual port control logic to allow the iSBC 86/12 board to act as a slave RAM device to other MULTIBUS masters in the system. Provision is made for user installation of up to 16K bytes of read only memory. Figure 1 contains a block diagram of the iSBC 86/12 board and in Appendix A is a simplified logic diagram of the iSBC 86/12 board.

### Central Processing Unit

The central processor for the iSBC 86/12 board is Intel's 8086, a powerful 16-bit H-MOS device. The 225 sq. mil chip contains 29,000 transistors and has a clock rate of 5MHz. The architecture includes four (4) 16-bit byte addressable data registers, two (2) 16-bit memory base pointer registers and two (2) 16-bit index registers, all accessed by a total of 24 operand addressing modes for complex data handling and very flexible memory addressing.

Instruction Set — The 8086 instruction repertoire includes variable length instruction format (including double operand instructions), 8-bit and 16-bit signed and unsigned arithmetic operators for binary, BCD and unpacked ASCII data, and iterative word and byte string manipulation functions. The instruction set of the 8086 is a functional superset of the 8080A/8085A family and with

Figure 1. iSBC™ 86 / 12 Single Board Computer Block Diagram

available software tools, programs written for the 8080A/8085A can be easily converted and run on the 8086 processor.

**Architectural Features** — A 6-byte instruction queue provides pre-fetching of sequential instructions and can reduce the  $1.2\,\mu$  sec minimum instruction cycle to 400 nsec by having the instruction already in the queue.

The stack oriented architecture facilitates nested sub-routines and co-routines, reentrant code and powerful interrupt handling. The memory expansion capabilities offer a 1 megabyte addressing range. The dynamic relocation scheme allows ease in segmentation of pure procedure and data for efficient memory utilization. Four segment registers (code, stack, data, extra) contain program loaded offset values which are used to map 16-bit addresses to 20-bit addresses. Each register maps 64K-bytes at a time and activation of a specific register is controlled explicitly by program control and is also selected implicitly by specific functions and instructions.

### **Bus Structure**

The iSBC 86/12 board has an internal bus for communicating with on-board memory and I/O options, a system bus (the MULTIBUS) for referencing additional memory and I/O options, and the dual-port bus which allows access to RAM from the on-board CPU and the MULTIBUS System Bus. Local (on-board) accesses do not require MULTIBUS communication, making the system bus available for use by other MULTIBUS masters (i.e. DMA devices and other single board computers transferring to additional system memory). This feature allows true parallel processing in a multiprocessor environment. In addition, the MUL-TIBUS interface can be used for system expansion through the use of other 8- and 16-bit iSBC computers, memory and I/O expansion boards.

### **RAM Capabilities**

The iSBC 86/12 board contains 32K-bytes of dynamic read/write memory. Power for the on-board RAM and refresh circuitry may be optionally provided on an auxiliary power bus, and

memory protect logic is included for RAM battery backup requirements. The iSBC 86/12 board contains a dual port controller which allows access to the on-board RAM from the iSBC 86/12's CPU and from any other MULTIBUS master via the system bus. The dual port controller allows 8- and 16-bit accesses from the MULTIBUS System Bus and the on-board CPU transfers data to RAM over a 16-bit data path. Priorities have been established such that memory refresh is guaranteed by the onboard refresh logic and that the on-board CPU has priority over MULTIBUS requests for access to RAM. The dual-port controller includes independent addressing logic for RAM access from the on-board CPU and from the MULTIBUS system bus. The on-board CPU will always access RAM starting at location 00000H. Address jumpers allow onboard RAM to be located starting on any 8K-byte boundary within a 1 megabyte address range for accesses from the MULTIBUS system bus. In conjunction with this feature, the iSBC 86/12 board has the ability to protect on-board memory from MULTIBUS access to any contiguous 8K-byte segments. These features allow multi-processor systems to establish local memory for each processor and shared system (MULTIBUS) memory configurations where the total system memory size (including local on-board memory) can exceed 1 megabyte without addressing conflicts.

### **EPROM/ROM Capabilities**

Four sockets are provided for up to 16K-bytes of non-volatile read only memory on the iSBC 86/12 board. Configuration jumpers allow read only memory to be installed in 2K, 4K, or 8K increments.

On-board ROM is accessed via 16 bit data paths. System memory size is easily expanded by the addition of MULTIBUS compatible memory boards available in the iSBC 80/86 family.

### Parallel I/O Interface

The iSBC 86/12 board contains 24 programmable parallel I/O lines implemented using the Intel 8255A Programmable Peripheral Interface. The system software is used to configure the I/O lines in any combination of unidirectional input/output and bidirectional ports.

Therefore, the I/O interface may be customized to meet specific peripheral requirements. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the I/O interface is further

enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. The 24 programmable I/O lines and signal ground lines are brought out to a 50-pin edge connector that mates with flat, woven, or round cable.

### Serial I/O

A programmable communications interface using the Intel 8251A Universal Synchronous/Asynchronous Receiver/Transmitter (USART) is contained on the iSBC 86/12 board. A software selectable baud rate generator provides the USART with all common communication frequencies. The USART can be programmed by the system software to select the desired asynchronous or synchronous serial data transmission technique (including IBM Bi-Sync). The mode of operation (i.e., synchronous or asynchronous), data format, control character format, parity, and baud rate are all under program control. The 8251A provides full duplex, double buffered transmit and receive capability. Parity, overrun, and framing error detection are all incorporated in the USART. The RS232C compatible interface on each board, in conjunction with the USART, provides a direct interface to RS232C compatible terminals, cassettes, and asynchronous and synchronous modems. The RS232C command lines, serial data lines, and signal ground line are brought out to a 26 pin edge connector that mates with RS232C compatible flat or round cable. The iSBC 530 teletypewriter adapter provides an optically isolated interface for those systems requiring a 20 mA current loop. The iSBC 530 adapter may be used to interface the iSBC 86/12 board to teletypewriters or other 20 mA current loop equipment.

### **Programmable Timers**

The iSBC 86/12 board provides three independent, fully programmable 16-bit interval timers/event counters utilizing the Intel 8253 Programmable Interval Timer. Each counter is capable of operating in either BCD or binary modes. Two of these timers/counters are available to the systems designer to generate accurate time intervals under software control. Routing for the outputs and gate/trigger inputs of two of these counters is jumper selectable. The outputs may be independently routed to the 8259A Programmable Interrupt Controller and to the I/O line drivers associated with

the 8255A Programmable Peripheral Interface, or may be routed as inputs to the 8255A chip. The gate/trigger inputs may be routed to 1/O terminators associated with the 8255A or as output connections from the 8255A. The third interval timer in the 8253 provides the programmable baud rate generator for the iSBC 86/12 RS232C USART serial port. In utilizing the iSBC 86/12, the systems designer simply configures, via software, each timer independently to meet system requirements. Whenever a given time delay or count is needed, software commands to the programmable timers/event counters select the desired function.

The contents of each counter may be read at any time during system operation with simple read operations for event counting applications, and special commands are included so that the contents can be ready "on the fly".

### MULTIBUS™ and Multimaster Capabilities

The MULTIBUS system bus features asynchronous data transfers for the accommodation of devices with various transfer rates while maintaining maximum throughput. Twenty address lines and sixteen separate data lines eliminate the need for address/data multiplexing/demultiplexing logic used in other systems, and allow for data transfer rates up to 5 megawords/sec. A failsafe timer is included in the iSBC 86/12 board which can be used to generate an interrupt if an addressed device does not respond within 6 msec.

Multimaster Capabilities — The iSBC 86/12 board is a full computer on a single board with resources capable of supporting a great variety of OEM system requirements. For those applications requiring additional processing capacity and the benefits of multiprocessing (i.e., several CPUs and/or controllers logically sharing system tasks through communication over the system bus), the iSBC 86/ 12 board provides full MULTIBUS arbitration control logic. This control logic allows up to three iSBC 86/12 boards or other bus masters, including iSBC 80 family MULTIBUS compatible 8-bit single board computers, to share the system bus in serial (daisy chain) priority fashion, and up to 16 masters to share the MULTIBUS with the addition of an external priority network. The MULTIBUS arbitration logic operates synchronously with a MULTI-BUS clock (provided by the iSBC 86/12 board or optionally provided directly from the MULTIBUS System Bus) while data is transferred via a handshake between the master and slave modules. This allows different speed controllers to share resources on the same bus, and transfers via the bus proceed asynchronously. Thus, transfer speed is dependent on transmitting and receiving devices only. This design prevents slow master modules from being handicapped in their attempts to gain control of the bus, but does not restrict the speed at which faster modules can transfer data via the same bus. The most obvious applications for the master-slave capabilities of the bus are multiprocessor configurations, high speed direct memory access (DMA) operations, and high speed peripheral control, but are by no means limited to these three.

### Interrupt Capability

The iSBC 86/12 board provides 9 vectored interrupt levels. The highest level is the NMI (Non-Maskable Interrupt) line which is directly tied to the 8086 CPU. This interrupt cannot be inhibited by software and is typically used for signalling catastrophic events (e.g., power failure).

The Intel 8259A Programmable Interrupt Controller (PIC) provides vectoring for the next eight interrupt levels.

The PIC accepts interrupt requests from the programmable parallel and serial I/O interfaces, the programmable timers, the system bus, or directly from peripheral equipment. The PIC then determines which of the incoming requests is of the highest priority, determines whether this request is of higher priority than the level currently being serviced, and, if appropriate, issues an interrupt to the CPU. Any combination of interrupt levels may be masked, via software, by storing a single byte in the interrupt mask register of the PIC. The PIC generates a unique memory address for each interrupt level. These addresses contain unique instruction pointers and code segment offset values (for expanded memory operation) for each interrupt level. In systems requiring additional interrupt levels, slave 8259A PIC's may be interfaced via the MULTIBUS system bus, to generate additional vector addresses, yielding a total of 65 unique interrupt levels.

**Interrupt Request Generation**—Interrupt requests may originate from 16 sources. Two jumper selectable interrupt requests can be automatically generated by the programmable peripheral interface.

Two jumper selectable interrupt requests can be automatically generated by the USART when a character is ready to be transferred to the CPU or a character is ready to be transmitted.

A jumper selectable request can also be generated by each of the programmable timers. Eight additional interrupt request lines are available to the user for direct interface to user designated peripheral devices via the system bus, and two interrupt request lines may be jumper routed directly from peripherals via the parallel I/O driver/terminator section.

### **Power-Fail Control**

Control logic is also included to accept a power-fail interrupt in conjunction with the AC-low signal from the iSBC 635 Power Supply or equivalent.

### **Expansion Capabilities**

Memory and I/O capacity may be expanded and additional functions added using Intel MULTIBUS compatible expansion boards. High speed integer and floating point arithmetic capabilities may be added by using the iSBC 310 high speed mathematics unit. Memory may be expanded to 1 megabyte by adding user specified combinations of RAM boards, EPROM boards, or combination boards. Input/output capacity may be increased by adding digital I/O and analog I/O expansion boards. Mass storage capability may be achieved by adding single or double density diskette controllers. Modular expandable backplanes and cardcages are available to support multiboard systems.

### III. THE iSBC™ 957 PACKAGE

The iSBC 957 Intellec-iSBC 86/12 Interface and Execution Package extends the software development capabilities of the Intellec Microcomputer Development systems to the Intel 8086 CPU. Programs for the 8086 may be written in PL/M-86 and/or assembly language and compiled or assembled on the Intellec system. These programs may then be downloaded from an Intellec ISIS-II disk file to the iSBC 86/12 board for execution and debug. The programs will execute at the full 5 MHz clock rate of the 8086 CPU with no speed degradation caused by the iSBC 957 hardware or software. Special communication software allows transparent access to the powerful interactive debug commands in the iSBC 86/12 monitor from the Intellec console terminal. These debug commands include single-step instruction execution, execution with breakpoints, memory and register displays, memory searches, comparison of two memory blocks and several other commands. After a debugging session, the debugged program code may be uploaded from the iSBC 86/12 board to an Intellec ISIS-II disk file.

The iSBC 957 Intellec—iSBC 86/12 Interface and Execution Package consists of the following:

- a. Four Intel 2716 EPROMs which contain the system monitor program for the iSBC 86/12 board.

- b. An ISIS-II diskette containing loader software for execution in the Intellec which provides for communications between the user or an Intellec ISIS-II file and the iSBC 86/12 board. Also included on the diskette are a library of routines for system console I/O.

- c. Four cable assemblies used for transmitting commands, code and data between the iSBC 86/12 board and the Intellec system.

- d. An iSBC 530 adapter assembly which converts serial communications signals from current loop to RS232C.

- e. Line drivers and terminators used for the iSBC 86/12 parallel ports.

- f. A small printed circuit board which is plugged into an iSBC 86/12 receiver/terminator socket and is used when program code is downloaded or uploaded using the parallel cable.

### iSBC<sup>™</sup>—Intellec<sup>™</sup> Configurations

There are two distinct functional configurations for the iSBC 957 package; one configuration for the Intellec Series II, Models 220 or 230 development systems and another for the Intellec 800 series development systems.

### **Intellec Series II System Configurations**

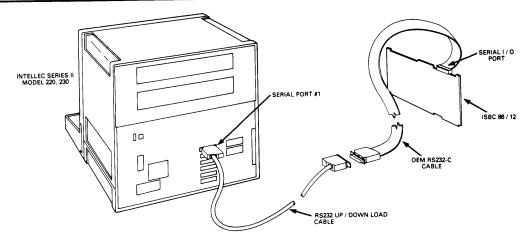

When used with Intellec Series II Model 220 or 230 systems, a set of cables are used to connect the serial I/O port edge connector on the iSBC 86/12 board and the SERIAL 1 output port on the Intellec system. This configuration is shown in Figure 2. How this system functions is explained in the following paragraphs.

The SERIAL 1 port on the Intellec Series II Model 220 or 230 system is an RS232 port which is designed for use with a data terminal. This port may be used on the Intellec system for interfacing to RS232 devices such as CRT terminals or printers. The serial ports on the iSBC 86/12 board and the Intellec systems are connected as shown in the Figure 2. The flat ribbon cable connected to the iSBC 86/12 board has an edge connector for connecting to the board on one end and a standard RS232 connector on the other end. The second cable, the RS232 Up/Down Load cable, has an RS232 connector on each end. This cable, however,

Figure 2. Intellec™ Series II Model 220, 230—iSBC™ 86 / 12 Configuration

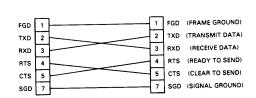

is not a standard cable with the RS232 signals bussed between identically numbered pins on each of the connectors. The schematic for the cable is shown in Figure 3. Note that the TXD (transmit data) and the RXD (receive data) and the RTS (ready to send) and the CTS (clear to send) signals have been crossed. This is done because both the Intellec system and the iSBC 86/12 board are configured to act as data sets which are communicating with data terminals. Swapping these signals permits the units to communicate directly with no modifications to the Intellec or iSBC 86/12 systems themselves.

Figure 3. Intellec<sup>™</sup>—iSBC<sup>™</sup> 86 / 12 RS232 UP / DOWN LOAD Cable

The software in the Intellec system accepts characters output from the iSBC 86/12 board through the Intellec SERIAL 1 port. The software then outputs these characters on the CRT monitor built into the Intellec Series II Model 220 or 230. In a similar fashion, characters input from the Intellec key-

board are passed down the serial link to the iSBC 86/12 monitor program. The integrated CRT monitor and keyboard on the Intellec system then becomes the "virtual terminal" of the iSBC 86/12 monitor program. If this were the only function of the iSBC 957 package, there would be no real benefit to the user. However, when the "virtual terminal" capability is combined with the capability to download and upload program code and data files between the Intellec ISIS-II file system and the iSBC 86/12 board, a very powerful software development tool is realized. The software in the Intellec system must examine the commands which are input from the keyboard and in the case of the LOAD and TRANSFER commands (see later sections for details on monitor commands), the software must open and read or write ISIS-II disk files.

Transfer rates using Intellec Series II Model 220 or 230 system are 9600 baud when transferring hexadecimal object files to or from a disk file and 600 baud when transferring commands between the iSBC 86/12 board and the CRT monitor and keyboard. With a 9600 baud transfer rate, it is possible to load 64K bytes of memory in about four minutes.

### **Intellec 800 System Configurations**

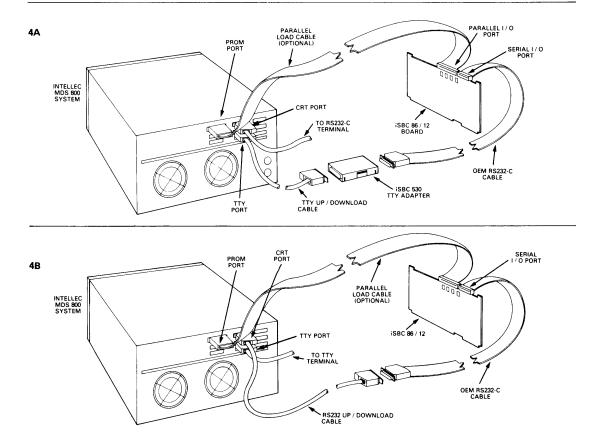

The iSBC 957 package may be used with the Intellec 800 system in four different configurations. These four configurations are determined by two

variables. The first variable is whether the iSBC 86/12 board is connected to the Intellec 800 TTY port or to the Intellec 800 CRT port. The second variable is whether or not a parallel cable is used for uploading and downloading hexadecimal object files. Figures 4A and 4B illustrate the four configurations.

In Figure 4A, the configuration shows the TTY port of the Intellec 800 system connected to the iSBC 86/12 serial port using two cables and an iSBC 530 teletypewriter adapter. The TTY port of the Intellec 800 system is designed for using a teletypewriter as the Intellec console device. To use this port for communication with the iSBC 86/12 board, the current loop TTY signal must be converted to an RS232 compatible voltage signal. This function is performed by the iSBC 530 adapter.

The cable which connects the Intellec 800 system to the iSBC 530 adapter performs a function similar to the RS232 Up/Down Load cable described above. A schematic for this cable and all other components of the iSBC 957 package are included with the delivered product.

The transfer rate for both commands and data when the TTY port is connected to the iSBC 86/12 board is 110 baud. This means to download even moderately sized programs would require large amounts of time, several minutes or even hours. However, much faster times may be achieved by using the parallel ports of the iSBC 86/12 board and the Intellec system for downloading program files. This parallel port used on the Intellec 800 system is the output port labeled PROM which is normally used with the Universal Prom Pro-

Figure 4A, 4B. Intellec™ 800 — iSBC™ 86 / 12 Configurations

grammer. A cable is connected between the Intellec PROM port and the parallel I/O port, J1 of the iSBC 86/12 board. Parallel port B of the iSBC 86/12 board is used for the 8-bit byte transfers from the Intellec system to the iSBC 86/12 board, port A is used for the byte transfers from the iSBC 86/12 board to the Intellec system and port C is used for controlling the byte transfers. A special status adapter piggyback board must be inserted into a receiver/terminator socket of the iSBC 86/12 board. This status adapter circuit is required to provide the necessary handshaking signals from the iSBC 86/12 parallel ports to the Intellec PROM port.

The transfer rate achieved when downloading and uploading hexadecimal object files with the parallel cable is approximately 1,000 bytes per second. The time required to load 64K bytes of memory is approximately  $2\frac{1}{2}$  minutes.

Figure 4B shows a configuration with the Intellec 800 CRT port connected to the serial port of the iSBC 86/12 board. The TTY port of the Intellec 800 system is connected to a teletypewriter or some other current loop device to act as a system console. The optional parallel load cable is also shown. The cables used for this configuration are the same as those used with the Intellec Series II Configurations. Command transfer rates require 110 baud because the TTY port of the Intellec 800 system is used for communicating with the console device. However, hexadecimal object files can be loaded at 9600 baud since this operation uses only the Intellec to iSBC 86/12 RS232 link.

It is also possible to download files with the parallel cable, this mode being somewhat faster than the serial download mode (2½ minutes versus four minutes for 64K bytes of memory). Table I contains a summary of the command and memory transfer rates for each of the Intellec-iSBC 86/12 configurations.

Comparing the Intellec 800 configurations shown in Table 1 and in Figures 4A and 4B it should be noted:

- Using the TTY port (Figure 4A) of the Intellec 800 system for communications with the iSBC 86/12 board (essentially) requires installation of the parallel cable and jumper modifications for downloading and uploading files, and thus, prevents the use of the parallel ports for other I/O functions.

- 2. Using the CRT port (Figure 4B) of the Intellec

800 system for communication with the iSBC 86/12 board provides for a fast serial download capability, thus freeing the parallel ports for other uses. However, this configuration requires a teletypewriter or a CRT capable of accepting a current loop input signal as the Intellec system console.

Table 1

COMMAND AND MEMORY TRANSFER RATES FOR

INTELLEC—ISBC™ 86 / 12 CONFIGURATIONS

|                                                                          | INTELLEC<br>SERIES II 220/230<br>SERIAL PORT<br>TO ISBC 86/12 | INTELLEC 800<br>TTY PORT<br>TO ISBC 96/12 | INTELLEC 800<br>CRT PORT<br>TO ISBC 86 / 12 |

|--------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|---------------------------------------------|

| Effective<br>Command Rate                                                | 600 Baud                                                      | 110 Baud                                  | 110 Baud*                                   |

| Load / Transfer<br>Rate<br>Serial<br>Parallel                            | 9600 Baud<br>N / A                                            | 110 Baud<br>1K bytes / sec**              | 9600 Baud<br>1K bytes/sec**                 |

| Approximate Time<br>to load 64K bytes<br>of memory<br>Serial<br>Parallel | 4 minutes<br>N / A                                            | 5 hours<br>2.5 minutes                    | 4 minutes<br>2.5 minutes                    |

<sup>\*</sup>The actual baud rate of the Intellec—iSBC 86 / 12 link is 9600 baud, but the effective command rate is determined by the slower Intellec—console serial link.

# IV. THE iSBC 957—iSBC 86/12 MONITOR PROGRAM

The iSBC 86/12 monitor program is an EPROM resident program which facilitates debugging of user written programs. The monitor program used in the iSBC 86/12 board with the iSBC 957 package is the same monitor program written to interface the iSBC 86/12 directly to an RS232C data terminal. When interfaced directly to a terminal, the iSBC 86/12 board functions in a stand-alone environment communicating directly with the user via the data terminal. A user may use the monitor for entering small programs in hexadecimal format, executing a program, examining registers and memory contents, etc.

To use the monitor program with an Intellec system, the proper cables must be installed and the iSBC 957 Loader program must be loaded into Intellec memory and executed. The Loader program is resident on a file named SBC861, and when executed, the Loader outputs a sign-on message. Next, the iSBC 86/12 monitor program must be started and the baud rate of the iSBC 86/12 to Intellec serial communications link must be determined. This is done by pressing the RESET switch on the chassis

<sup>\*\*</sup>Transmission rate over the parallel link is determined by the speed of the two processors and is approximately 1K bytes per second.

Table 2

MONITOR COMMAND LIST

|                               | MONTON COMMAND LICT                                                                                                  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------|

| COMMAND                       | FUNCTION AND SYNTAX                                                                                                  |

| L Load Hex<br>Object File     | Loads hexadecimal object file from Intellec into iSBC 86/12 memory using serial (S) or parallel (P) mode.            |

|                               | L(S P), filename>[, bias addr>] <cr></cr>                                                                            |

| T Transfer Hex<br>Object File | Transfers blocks of iSBC 86/12 memory to Intellec as a hex object file using serial (S) or parallel (P) mode.        |

|                               | T(X) {S P} , <start addr="">,<end addr="">,<filename><br/>[,<exec addr="">]<cr></cr></exec></filename></end></start> |

| E Exit                        | Exits the loader program and returns to ISIS.                                                                        |

|                               | E <cr></cr>                                                                                                          |

| N Single Step                 | Executes one user program instruction.                                                                               |

|                               | N( <addr>),((<addr>),(*<cr></cr></addr></addr>                                                                       |

| G Go                          | Transfers control of the 8086 CPU to the user program with up to 2 optional breakpoints.                             |

|                               | G[ <start addr="">][,<break 1="" addr=""></break></start>                                                            |

|                               | (, <break 2="" addr="">) <cr></cr></break>                                                                           |

| S Substitute<br>Memory        | Displays/modifies memory locations in byte or word format.                                                           |

|                               | S[W] <addr>,[[new contents],]*<cr></cr></addr>                                                                       |

| X Examine/Modify              | Displays/modifies 8086 CPU registers.                                                                                |

| Register                      | X[ <reg>][(<new contents="">],]*<cr></cr></new></reg>                                                                |

| D Display Memory              | Displays contents of a memory block in byte or word format.                                                          |

|                               | D(W) <start addr="">(,<end addr="">)<cr></cr></end></start>                                                          |

| M Move                        | Moves contents of a memory block.                                                                                    |

|                               | M <start addr="">,<end addr="">,<destination addr=""><cr></cr></destination></end></start>                           |

| C Compare                     | Compares two memory blocks.                                                                                          |

|                               | C <start addr="">,<end addr="">,<destination addr=""><cr></cr></destination></end></start>                           |

| F Find                        | Searches a memory block for a byte or word constant.                                                                 |

|                               | F(W)< start addr>,< end addr>,< data> < cr>                                                                          |

| H Hex Arithmetic              | Performs hexadecimal addition and subtraction.                                                                       |

|                               | H <data 1="">,<data 2=""><cr></cr></data></data>                                                                     |

| I Port Input                  | Inputs and displays byte or word data from input port.                                                               |

|                               | [W] <port addr="">,[,]*<cr></cr></port>                                                                              |

| O Port Output                 | Outputs byte or word data to output port.                                                                            |

|                               | O[W] <port addr="">,<data>[,<data>]*<cr></cr></data></data></port>                                                   |

|                               |                                                                                                                      |

Syntax conventions used in the command structure are as follows:

(A) indicates that "A" is optional

[A]\* indicates one or more optional iterations of "A"

<B> indicates that "B" is a variable

{A|B} indicates "A" or "B"

<cr> indicates a carriage return is entered

Numeric arguments can be expressed as a number, the contents of a register, or the sum or difference of numbers and register contents. Thus, addresses and data can be expressed as follows:

$\begin{array}{lll} \textit{eddr} ::= & \{ < \exp r > : \} < \exp r \\ & = \exp r ::= & < number > \{ register > \{ expr > \{ + \mid - \} < number > \mid \\ & < \exp r > \{ + \mid - \} < register > \\ & register ::= & AX \mid BX \mid CX \mid DX \mid SP \mid BP \mid SI \mid DI \mid CS \mid DS \mid SS \mid ES \mid P \mid FL \\ & number ::= & c digit > 1 < digit > c digit > c light > c$

Numeric fields within arguments are entered as hexadecimal numbers. The valid range of numerical values is from 0000-FFFF. Larger numbers may be entered, but only the last four digits (or two in the case of byte values) are significant. Leading zeros may be omitted.

An address argument consists of a segment value and an offset value separated by a colon (:). If a segment value is not specified, the default segment value is the CS register value.

containing the iSBC 86/12 board and typing two "U"s on the Intellec console. The ASCII uppercase character U has a binary pattern of alternating ones and zeros, the iSBC 86/12 monitor uses this pattern to determine the baud rate of the serial link. After the baud rate has been determined, the monitor program outputs a sign-on message to the console. An example of loader program execution and monitor program initialization is shown below (user entered characters are underlined).

### :F1:SBC861

ISIS-II iSBC 86/12 LOADER, Vx.x (user resets iSBC 86/12 board and types two "U"s) iSBC 86/12 MONITOR, Vy.y

The monitor prompts with a period "." when it is ready for a command. The user can then enter a command file, which consists of a one- or two-character command followed by zero, one, or more arguments. The command may be separated from the first argument by an optional single space; a single comma is required as a delimiter between arguments. The command line is terminated by a carriage return or a comma depending on the command, and no action takes place until the command terminator is sensed. The user can cancel a command before entering the command terminator by pressing any illegal key (e.g., rubout or Control-X).

Table 2 contains a summary of the loader and monitor commands. These commands will not be explained in detail; instead, the next section of the application note will show examples of using these loader and monitor commands. The iSBC 957 User's Guide referenced at the front of this document does, however, contain a complete description of each of the monitor and loader commands.

Table 3 contains a list of the 8086 hardware registers and abbreviations used by the monitor program.

Table 3 8086 CPU REGISTERS

| REGISTER NAME       | ABBREVIATION |

|---------------------|--------------|

| Accumulator         | AX           |

| Base                | BX           |

| Count               | cx           |

| Data                | DX           |

| Stack Pointer       | SP           |

| Base Pointer        | BP           |

| Source Index        | SI           |

| Destination Index   | DI           |

| Code Segment        | cs           |

| Data Segment        | DS           |

| Stack Segment       | SS           |

| Extra Segment       | ES           |

| Instruction Pointer | IP           |

| Flag                | FL           |

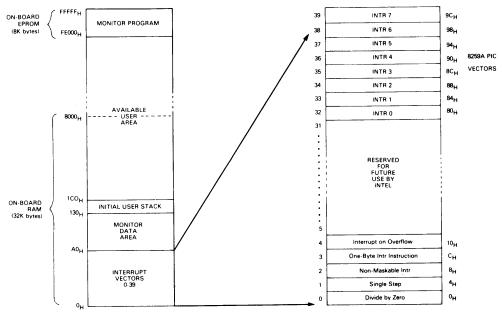

Figure 5. Memory Map of iSBC™ 86 / 12 Memory With Monitor Program

Figure 5 contains a memory map of the iSBC 86/12 memory with the monitor program. Note that the monitor uses the top 8K bytes of memory for its program code and the first 384 bytes of memory (locations Ø hex to 17F hex) for monitor and user stack, data and interrupt vectors. When the monitor program is reset, the segment registers, the IP and the flags are set to 0; and the SP is set to 01C0H allowing 64 bytes for the user's stack. If 64 bytes is not sufficient for the user's application program, the SP should be set to some other value. The monitor program sets the single-step, one-byte instruction trap and non-maskable interrupt vectors to monitor entry points. The monitor also sets the 8259A Priority Interrupt Controller to fully nested mode with level 0 at the highest priority and all interrupts unmasked. The eight interrupt vector addresses for the 8259A are also set to addresses in the monitor. User programs may change the 8259A interrupt vectors to interrupt service routine addresses within the user programs; it is not necessary for users to program the 8259A chip directly. When an interrupt occurs, control passes to either the monitor or directly to user code depending on the address stored in the vector location. When the monitor responds to an interrupt, it acknowledges the interrupt and displays the interrupt level, CS and IP register values and next instruction byte on the system console (e.g., I = 3 @ 100:230F F5).

When a user requests a breakpoint with a "G" command, the monitor inserts the single byte instruction trap instructions (INT 3) in the location where the breakpoint is requested. It is also possible for the user to code an INT 3 instruction in his program. When a user coded INT 3 instruction is executed, the monitor will be re-entered and a line with the format @<CS Value>:<IP Value> <Instruction byte> will be displayed (e.g., @1200:3FO2 F5).

Included on the diskette with the Loader program are two libraries containing I/O routines for the console. The library files are named SBCIOS.LIB and SBCIOL.LIB; they contain similar routines. The routines in SBCIOS.LIB are written to be called with intrasegment subroutine calls, a PL/M-86 module compiled with the "small" control generates this type of call. The routines in SBCIOL.LIB are written to be called with intersegment subroutine calls, a PL/M-86 module compiled with either the "medium" or "large" control generates this type of call.

The console input output routines, CI and CO, contained in the library should be used when performing character input and output on the console. Example PL/M-86 calls to the two routines are:

CI: PROCEDURE BYTE EXTERNAL;

END CI;

CO: PROCEDURE (X) EXTERNAL;

DECLARE X BYTE;

END CO;

...

DECLARE INPUT\$CHAR,

OUTPUT\$CHAR BYTE;

...

...

INPUT\$CHAR = CI;

...

...

CALL CO(OUTPUT\$CHAR);

# General Comments on Use of the iSBC 957 Package

- 1. If the iSBC 86/12 board is reset any time after the initial baud rate search, it is not necessary to reload the iSBC 957 Loader program or to download the program code a second time to the iSBC 86/12 board. It is only necessary to reestablish the communications link by typing two "U"s for the baud rate search.

- 2. The iSBC 86/12 board should not be plugged into an available card slot in an Intellec chassis; a separate chassis should be used. There are at least three reasons for this:

- a. There is only one RESET signal available on the Intellec system bus. Thus, each processor may not be reset independently. This means that the iSBC 86/12 board cannot be reset without re-booting the ISIS-II operating system and restarting the iSBC 957 Loader.

- b. The Intellec system uses five of the eight available interrupts on the system bus. This severely restricts the range of interrupts available to the iSBC 86/12 board. Also, the iSBC 86/12 board cannot turn-off the interrupt lamps on the Intellec front panel.

- c. The iSBC 86/12 board may address up to 1 Megabyte of memory using a 20 bit address. Many Intellec systems contain boards which generate and decode only the low order 16 address bits. For example, the iSBC 016 memory expansion board and the Intellec 800

- monitor PROMs only decode 16 address bits. Memory expansion above 64K bytes in these systems is difficult since the boards which decode only 16 bits will force "holes" in the address space above 64K.

- 3. The iSBC 86/12 board is delivered with two inputs to the 8259A Priority Interrupt Controller connected. Interrupt request 2 (IR2) is connected to the counter Ø output of the 8253 Programmable Interval Timer. IR5 is connected to the INT5/signal of the MULTIBUS System Bus. If these interrupts are not desired, the wire wrap jumpers making the connections should be removed from the iSBC 86/12 board. A particular problem may exist with the counter Ø connection to IR2. If the 8253 counter Ø is not specifically initialized with software, a low frequency square wave output will exist at counter Ø's output. This may cause unwanted interrupts when interrupts are enabled by user programs.

- 4. If the iSBC 86/12 board is used in a system with expansion boards, it is important that the MULTIBUS bus exchange pins be properly jumpered. For example, if the iSBC 86/12 board is used with an iSBC 032 expansion memory board in a system, the BPRN/ MULTIBUS pin for the iSBC 86/12 board should be grounded.

- In addition, if any interrupts are used with the iSBC 86/12 board the BPRN/ pin must be grounded. This is true in both single and multiple board systems.

- 5. Certain user systems require more than one single board computer in the system for performing the functions required by the application. The MUL-TIBUS System Bus has been specifically designed to permit multiple CPU boards to communicate and to share system resources. However, debugging systems with multiple CPUs has always posed somewhat of a problem. The iSBC 957 package provides a solution to this problem. The serial cable which connects the iSBC 86/12 board to the Intellec system may be removed after the program has been downloaded to the iSBC 86/12 board. A console CRT may then be connected directly to the iSBC 86/12 board and the monitor program may be used to debug the program running on the board. Other iSBC 86/12 boards may also be downloaded from the Intellec system and then switched to their own local terminals. An 8-bit processor board, such as the iSBC 80/30 board, may also be included

in the system and ICE-85™ may be used for debugging the iSBC 80/30 program concurrently with the iSBC 86/12 programs. Using this scheme, it is possible to debug a system which has several CPU boards by setting breakpoints and using other debugging features on each of the individual CPUs.

### V. MATRIX MULTIPLICATION EXAMPLE

To illustrate how the iSBC 957 package can be used to assist in the writing and debugging of 8086 programs on the iSBC 86/12 board, an example program of a matrix multiplication will be presented. The example chosen has been intentionally kept simple and straightforward. The emphasis of this section will be to document the steps required to assemble, compile, link, locate and debug software using an Intellec system, the iSBC 957 package and the iSBC 86/12 board. Part of the example will be written in 8086 assembly language and part in PL/M-86.

The main program is written in PL/M-86. The main program first performs some initialization and the matrix multiplication, then the program calls an assembly language procedure (subroutine), a PL/M-86 procedure and the console output procedure CO supplied in the I/O library on the iSBC 957 diskette. A flow diagram for the example program is shown in Figure 6.

### **Explanation of the Program Code**

The program code is contained in three software modules EXECUTION\$VEHICLE, FIND, and SBCCO. EXECUTION\$VEHICLE contains the main program coded in PL/M-86 and the binary to ASCII conversion procedure BIN\$DEC\$ASC also coded in PL/M-86. The module FIND contains the assembly language procedure FIND\$MX which searches a matrix for its maximum value. The module SBCCO resides in the library of console I/O routines supplied with the iSBC 957 package. The procedure CO will be used from this library.

The program code for the EXECUTION\$VEHICLE and FIND modules will be explained in the following paragraphs. Appendix B contains compilation and assembly listings for the two modules; also contained in Appendix B is a memory and debug map for the linked modules. The listings contain circled reference letters (e.g., (A)) which are referred to by the code description below. The listings in the appendix have been printed on fold-out pages so that they may easily be seen when reading the text.

Figure 6.

Flow Diagram of Matrix Multiplication Example

Much of the description given below assumes that the reader is familiar with the PL/M-86 language and compiler, the 8086 assembler, and the link and locate program QRL86. It is recommended that the reader have at least a cursory knowledge of these subjects. The Intel literature for these subjects is listed near the front of this application note.

### The EXECUTION\$VEHICLE Module

- A The first section of the module includes introductory comments and then statements to declare the matrices, other variables, and procedures used in the program. Note that the matrix dimensions are declared using the literals M, N, and P which are initially set to 6, 5, and 3. Later in this note, other values for M, N, and P will be used.

- B The next section of code contains the statements which initialize the two matrices that will be multiplied X\$ROW and Y\$ROW.

As a result of this initialization, the two matrices will contain values as shown in Figure 7.

$$\begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 1 & 1 & 1 & 1 & 1 \\ 2 & 2 & 2 & 2 & 2 \\ 3 & 3 & 3 & 3 & 3 \\ 4 & 4 & 4 & 4 & 4 \\ 5 & 5 & 5 & 5 & 5 \end{bmatrix}$$

X\$ROW (6X5)

Y\$ROW (5X3)

Figure 7.

X\$ROW and Y\$ROW Matrices After Initialization

C The next program section performs the matrix multiplication. The algorithm required to multiply two matrices X and Y, storing the result in a third matrix Z is:

$$Z_{mp} = \sum_{i=1}^{n} X_{mi} * Y_{ip}$$

Assuming X to be 6X5 matrix and Y a 5X3 matrix then

$$Z_{11} = X_{11}Y_{11} + X_{12}Y_{21} + X_{13}Y_{31} + X_{14}X_{41} + X_{15}Y_{51}$$

Thus, the upper left term is equal to the sum of the products of the top row of the X matrix times the left column of the Y matrix. The result that is obtained by multiplying the two matrices X\$ROW and Y\$ROW after they are initialized as explained above, is shown in Figure 8.

Z\$ROW (6X3)

Figure 8. Result of Multiplying the Initialized Matrices X\$ROW and Y\$ROW