Table of Contents

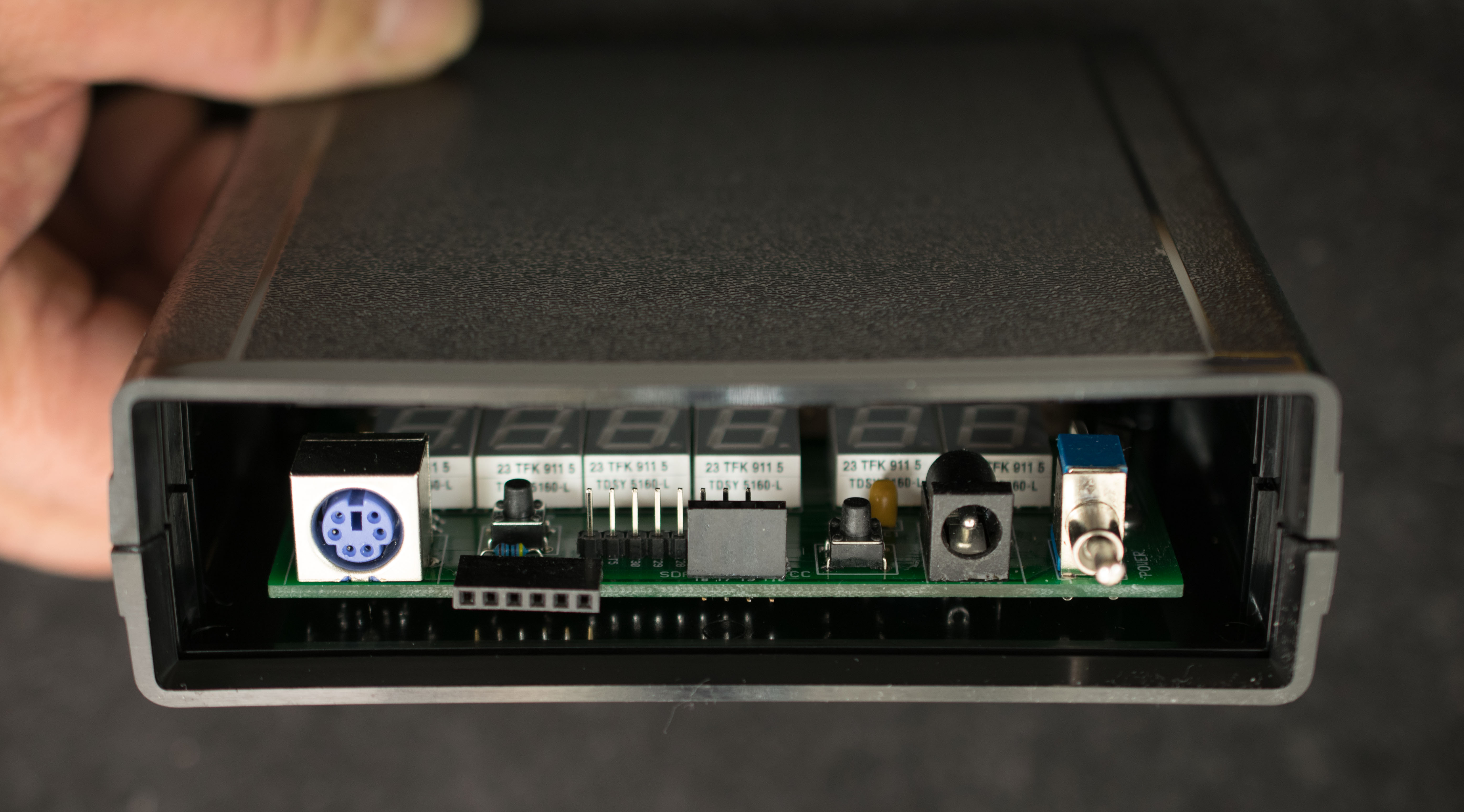

CPLD Educational Board with 6502 Processor, CPLD6502 Rev 0

Introduction

CPLD6502 explores the world of complex programmable logic device (CPLD) and how it interact with a 6502 processor and memories. Discussion about the CPLD6502 trainer can be found here. This is link to rev1 of CPLD Trainer.

Features

- EPM7128SLC84 128-macrocell CPLD

- W65C02 or W65C816 processor

- 128K RAM

- 128 EPROM

- Six 7-segment displays

- Serial port

- I2C interface

- SPI interface

- PS2 keyboard interface

- RC6502 expansion bus

- 100mm X 100mm 2-layer pc board

- PacTec CM5-125 enclosure

Design Information

CPLD design files for 6502SBC_Serial_V02

Software

CPLD6502 Monitor for 6502SBC_Serial_V02 CPLD design

Training Sessions

Design files and software for the various sessions

Jan 27, 2022 ,Session 1, Initial power up and first CPLD program. Session 1 CPLD design files

Jan 28, 2022, Session 2, multiplexing 7-segment displays. Session 2 CPLD design files

Jan 30, 2022, Session 3, 6-digit 7-segment display. Session 3 CPLD design files

Jan 31, 2022, Session 4, lookup table and true 6-digit hex display. Session 4 CPLD design files

Feb 1, 2022, Session 5, 6502 NOP test. Session 5 CPLD design files

Feb 2, 2022, Session 6, tester for 6502. Session 6 CPLD design files

Feb 3, 2022, Session 7, EPROM and RAM decode. Session 7 CPLD design files

Feb 4, 2022, Session 8, RAM diagnostic. RAM diagnostic source files

Feb 5, 2022, Session 9, 6502 SBC with serial port in CPLD. Session 9 CPLD design files

Feb 6, 2022, Session 10, Monitor for 6502 SBC. Session 10 CPLD design files, CPLD6502 SBC monitor software.

Projects

Feb 15, 2022, Flash Programmer project. CPLD design files, TeraTerm macro to load serial loader, SST algorithm, and data file