Table of Contents

SBC V2-005 MEGAFLASH

The SBC V2 is a Zilog Z80 processor board. It's a 100x160mm board that is capable of functioning both as a standalone SBC or as attached to the ECB bus.

The main advantage of this version over previous versions is the support of 1Mb FLASH memory and improved software support for Flash access.

The SBC V2-005 is transitioning from development to release. Development history and additional supporting information can be found here

Features

- 4Mhz+ Zilog Z80 CPU.

- 512Kb paged SRAM.

- 1Mb Flash ROM.

- Serial Interface.

- IDE interface.

- Real Time Clock.

- Onboard sound.

- Battery backup for RTC and SRAM via super capacitor.

- Standard ECB bus interface.

- +5V power connector for Single Board Computer operation.

- Reset button.

- Recovery mode button.

- Status LED.

- Switchable clock speed.

Software Support

ROMWBW BIOS featuring:

- CP/M / ZSDOS

- RAM & ROM disk support.

- ROM based BASIC, FORTH and Monitor.

- Prebuild disk images

ROMWBW Eurocard expansion board driver support:

- RAMFLOPPY - Up to 2 x 4Mb memory drives.

- VDU - Composite VDU monitor and keyboard support.

- CVDU - Colour VDU and keyboard support.

- VGA3 - Colour VGA display board and keyboard support

- Zilog Peripherals - 2xSerial ports, counter timer chip.

- USB FIFO - USB serial interface

- Disk I/O - 3.5“, 5-1.4”, 8“ floppy disk and parallel port IDE.

- 4PIO - Parallel interface card.

- SCG - Graphics and sound board.

- DUAL SD CARD - SD Card based memory drive

- MF-PIC - Colour VGA, keyboard interface.

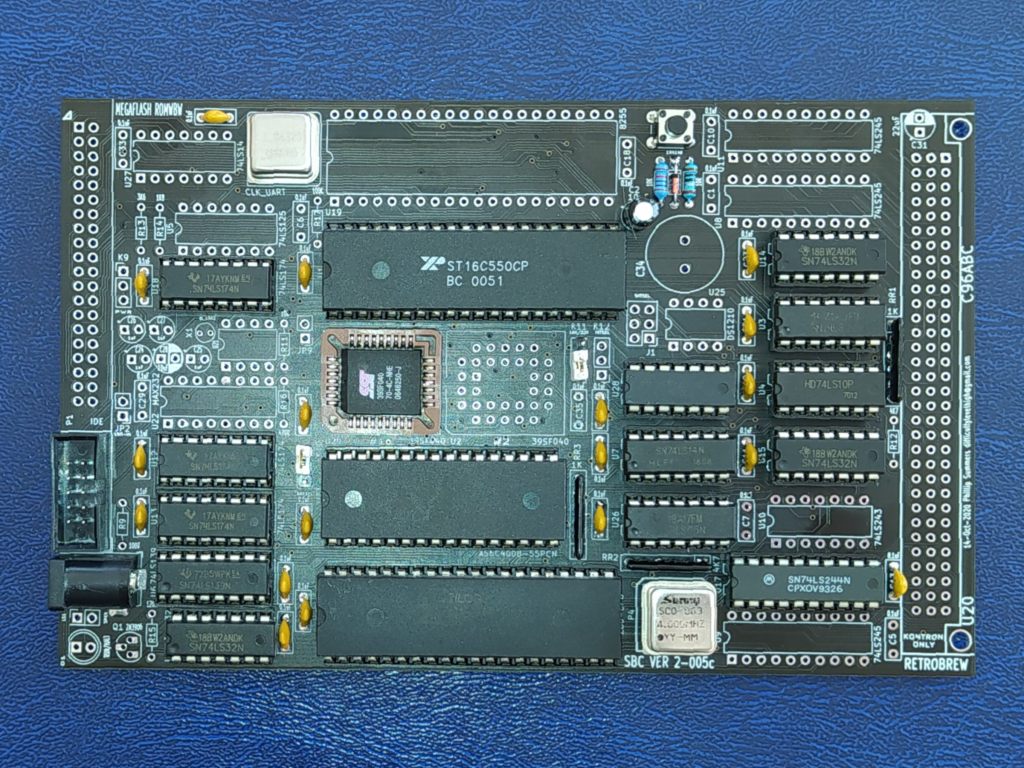

Pictures

Board

Kicad files can be found here but may not be the most recent.

Gerbers for SBC V2-005c, which have been built and tested. here.

Current revision is SBC V2-005i

Gerbers for SBC V2-005i, currently untested here.

Version i boards are on order as at 27-Feb-2021.

Changes from SBC V2-004

- Support 2 x 512Mb PLCC style Flash chips for 1Mb Flash memory.

- Removes support for DIP style Flash and EPROM chips.

- Removes support for 128Mb RAM

- Adds switch for recovery mode.

- Software support for programming dual chips.

- Driver support for accessing ROM drive as a read and write filesystem.

- ROMWBW based Flash upgrader.

- Solder link for UART clock as CPU clock for minimalist system.

Parts List

| Reference | # | Value | DIP8 | DIP14 | DIP16 | DIP20 | DIP32 | DIP40 | PLCC32 | |

|---|---|---|---|---|---|---|---|---|---|---|

| C1,C3-C23,C29,C30,C32,C33,C35 | 17 | 0.1uF | Ceramic Capacitor | |||||||

| C2 | 1 | 10uF | Electrolytic Capacitor | |||||||

| C24-C27 | 4 | 1uF | Electrolytic or Tantalum Capacitor | |||||||

| C28 | 1 | 10uF | Electrolytic Capacitor | |||||||

| C31 | 1 | 22uF | Electrolytic Capacitor | |||||||

| C34 | 1 | 0.22F+ | Super Capacitor | |||||||

| D1 | 1 | 5mm LED | Red/Green Bicolor | |||||||

| D2 | 1 | 1N4148 | Diode | |||||||

| K9-K12 | 4 | 1×3 | Pin Header 3 position 2.54mm | |||||||

| JP1 | 1 | 2×3 | Pin Header 2×3 position 2.54mm | |||||||

| JP2, LS1 | 4 | 1×2 | Pin Header 2 position 2.54mm | |||||||

| P1 | 1 | 2×20 | 40 pin IDC vertical socket. | |||||||

| P2 | 1 | 2.1mm | Barrel Jack Socket | |||||||

| P3 | 1 | 2×5 | 10 pin IDC vertical socket. | |||||||

| P4 | 1 | 4/8Mhz | CPU Clock 5V Active crystal oscillator square socket | 1 | ||||||

| P5 | 1 | 1.8432Mhz | UART Clock 5V Active crystal oscillator square | |||||||

| Q1 | 1 | 2N3906 | PNP Transistor | |||||||

| SW1, SW2 | 2 | 6x6mm | Mini Push Button Switch DIP 4pin | |||||||

| R1 | 1 | 10R | 0.25w resistor | |||||||

| R2,R11 | 2 | 10K | 0.25w resistor | |||||||

| R9 | 1 | 100R | 0.25w resistor | |||||||

| R12 | 1 | 4K7 | 0.25w resistor | |||||||

| R13 | 1 | 3K6 | 0.25w resistor | |||||||

| R14 | 1 | 1K8 | 0.25w resistor | |||||||

| R15 | 1 | 120R | 0.25w resistor | |||||||

| R16 | 1 | 470R | 0.25w resistor | |||||||

| R17 | 1 | 100K | 0.25w resistor | |||||||

| RR1, RR3 | 2 | 1K | SIP-6 Resistor array | |||||||

| RR2 | 1 | 4K7 | SIP-6 Resistor array | |||||||

| U1 | 1 | 16550 | UART DIP40 socket | 1 | ||||||

| U2 | 2 | 39SF040 | Flash 512kb PLCC32 socket | 2 | ||||||

| U3 | 1 | 74LS08 | Quad 2-in AND Gate DIP14 socket | 1 | ||||||

| U4 | 1 | 74LS10 | Triple 3-Input NAND Gate DIP14 socket | 1 | ||||||

| U5 | 1 | 74LS125 | Tri State Quad Bus Buffer DIP14 socket | 1 | ||||||

| U6 | 1 | 74LS139 | Dual 1-of-4 Decoder/De-multiplexer DIP16 socket | 1 | ||||||

| U7,U27 | 2 | 74LS14 | Hex Inverter/Schmitt Trigger DIP14 socket | 2 | ||||||

| U10 | 1 | 74LS243 | Quad Bus Transceiver DIP14 socket | 1 | ||||||

| U8,U9,U11 | 3 | 74LS245 | Octal tri-state bus transceiver DIP20 socket | 3 | ||||||

| U12,U13,U18 | 3 | 74LS174 | Hex D-type flip flop with clear DIP16 socket | 3 | ||||||

| U14-U16 | 3 | 74LS32 | Quad 2-input OR gate DIP14 socket | 3 | ||||||

| U17 | 1 | 74LS244 | Octal Driver Tri-State DIP20 socket | 1 | ||||||

| U19 | 1 | 8255 | Programmable Peripheral Interface DIP40 socket | 1 | ||||||

| U20 | 1 | C96ABC | DIN 41612 Connector, 96 pin plug, right angle. | |||||||

| U21 | 1 | DS1302 | Maxim Trickle-Charge Timekeeping Chip DIP8 socket | 1 | ||||||

| U22 | 1 | MAX232 | Maxim Multichannel RS-232 Drivers/Receiver DIP16 socket | 1 | ||||||

| U23 | 1 | AS6C4008 | 512Kb x 8 RAM DIP32 socket | 1 | ||||||

| U24 | 1 | Z84C00 | Z80 CPU DIP40 socket | 1 | ||||||

| U25 | 1 | DS1210 | Maxim Nonvolatile Controller Chip DIP8 socket | 1 | ||||||

| U26 | 1 | 74LS06 | Hex inverter buffers/drivers DIP14 socket | 1 | ||||||

| U28 | 1 | 74LS74 | Dual D-Type Positive Edge Triggered Flip Flop DIP 14 socket | 1 | ||||||

| X1 | 1 | 32.768KHz | 3mm Crystal 6pF | |||||||

| Sockets | 3 | 11 | 5 | 4 | 2 | 3 | 2 |

Minimum Build

Excludes Sound, RTC, IDE interface, Battery Backup controller and super capacitor, RS232 TTL converter, ECB bus interface, 2nd Flash ROM

| Reference | Component |

|---|---|

| C2 | 10uF |

| C3, C4, C9, C11-C17, C19-C23, C30, C32 | 0.1uF |

| D2 | 1N4148 |

| JP3-JP4 | SOLDER BRIDGE |

| JP4-JP8 | SOLDER BRIDGE |

| P2 | BARREL JACK |

| P3 | IDC SOCKET |

| P4 | 4-10MHz XTAL + SOCKET |

| P5 | 1.8432 XTAL |

| U1 | 16550 |

| U3 | 74LS08 |

| U4 | 74LS10 |

| U6 | 74LS139 |

| U7 | 74LS14 |

| U12, U13, U18 | 74LS174 |

| U14, U15, U16 | 74LS32 |

| U17 | 74LS244 |

| U23 | AS6C4008 |

| U24 | Z80CPU |

| U26 | 74LS06N |

| U28 | 74LS74 |

| U29 | 39SF040 |

| K10 | Pin Header, 1-2 BRIDGED |

| K11 | Pin Header, 1-2 BRIDGED |

| R1 | 10R |

| R2 | 10K |

| RR1, RR2 | 10K |

| RR3 | 4K7 |

| SW1 | Push Button |

SBC Build

Excludes ECB interface

| Reference | Component |

|---|---|

| C6, C18, C33, C35 | 0.1uF |

| C24-C27 | 1uF |

| C28 | 10uF |

| C34 | 0.22F-0.47F Super capacitor |

| D1 | BICOLOUR LED |

| JP1 | PIN HEADER |

| JP2 | PIN HEADER |

| JP3-JP4 | REMOVE SOLDER BRIDGE |

| JP5-JP8 | REMOVE SOLDER BRIDGE |

| JP9 | PIN HEADER |

| K9 | PIN HEADER (not requires version f+) |

| K12 | PIN HEADER, 2-3 BRIDGED |

| LS1 | PIN HEADER |

| P1 | IDC SOCKET |

| Q1 | 2N3906 |

| R9 | 100R |

| R11 | 10K |

| R12 | 4K7 |

| R13 | 3K6 |

| R14 | 1K8 |

| R15 | 120R |

| R16 | 470R |

| R17 | 100K |

| U2 | 39SF040 |

| U5 | 74LS125 |

| U19 | 8255 |

| U21 | DS1302 |

| U22 | MAX232 |

| U24 | DS1210 |

| U27 | 74LS14 |

| SW2 | Push Button (Revision f+) |

Full Build

| Reference | Component |

|---|---|

| C1, C5, C7, C10, | 0.1uF |

| C31 | 22uF |

| U8, U9, U11 | 74LS245 |

| U10 | 74LS243 |

| U20 | DIN EURO MALE RA 96 |

Boot ROM Installation

The firmware for the SBC V2 is called ROMWBW and can be obtained from Wayne Warthen's ROMWBW github repository.

Initial programming of the ROM requires the use of a programmer that supports Flash PLCC32 chips such as the MiniPro TL866II. Subsequent reprogramming can be done on the SBC V2 if you have enough secondary storage to hold the ROM image file. This is the preferred method as installing and removing the PLCC32 Flash chips is more difficult then the DIP32 style chips used previously.

Download the latest release i.e. RomWBW-v3.0.1-Package.zip and extract the ROM image file \Binary\SBC_std.rom. This is a 512Kb image and should be programmed to a 39SF040 (preferably) or AT49F040 and installed in flash location #1

Installing a 1Mb ROM image requires downloading, installing, customizing and assembling the ROMWBW source. Documentation on this process is detailed in \Source\ReadMe.txt file.

To assemble a 1024Kb ROMWBW rom, use the following as an example command line in the Source directory: build SBC std 1024 . The finished ROM image will be saved in the \Binary subdirectory. Before programming, split the file into 512Kb parts using a tool such as HxD.

MegaFlash Boot ROM configuration

The default configuration of ROMWBW is for the SBC V2-003 and includes the following driver options:

- Serial port.

- Real Time Clock

- Colour VDU board.

- VGA board.

- Parallel Port IDE.

- Propeller IO.

If the JP2 jumper “1BIT-IN” is bridged the default console will switch from Serial port to the first video card.

Some suggested configuration changes to take advantage of SBC V2-004+ features:

; SBCV2004 DEFINES A FLAG TO SWITCH TO HALF SPEED WHEN ACCESSING SOME SLOW DEVICE. #DEFINE SBCV2004 ; BEEP ON BOOT AND INCLUDE SOUND DRIVER. SPKENABLE .SET TRUE ; TRUE FOR RTC LATCH IOBIT SOUND ; RECOGNIZE THE RECMODE SWITCH ON BOOT TO LOAD MINIMAL DRIVER SET. BT_REC_TYPE .SET BT_REC_SBCRI ; SAFE MODE INPUT METHOD ; CHARGE SUPERCAPACITOR AND REPORT WHEN LOW DSRTCCHG .SET TRUE ; DSRTC: FORCE BATTERY CHARGE ON BATCOND .SET TRUE ; REPORT LOW BATTERY ON BOOT

Flash Programming

Will Sowerbutts has updated his FLASH4 program to support programming one or more flash chips. The updated Flash4 can be found in Will Sowerbutts github repository https://github.com/willsowerbutts/flash4 and is also included in the current development release of ROMWBW. As the RAM disk on the SBC V2 is smaller then 512Kb, the ROM image to be programmed must reside on an alternate storage device such an IDE flash card.

An example command line to update ROMWBW would be b:flash write std512.rom /1 or b:flash write cust1024.rom /2 for a 512Kb or 1024Kb ROM respectively.

Acknowledgement

The SBC V2-005 is based on the work of Andrew Lynch N8VEM and others in the Retrobrew Computers community. To see Andrew's foundation work, see here.

Thank you Andrew!

Contact

I can be contacted at difficultylevelhigh @ gmail.com or on the retrobrew computers forum as user b1ackmai1er